Questões de Concurso Militar CIAAR 2022 para Primeiro Tenente - Engenharia Eletrônica

Foram encontradas 28 questões

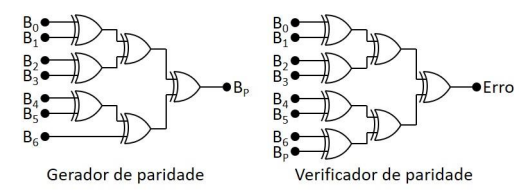

2O projetista de uma empresa foi encarregado de projetar um circuito gerador de paridade par para uma palavra de sete bits. Um outro projetista foi encarregado de projetar um circuito verificador de paridade para trabalhar com dados com paridade ímpar e que deve gerar um sinal de erro com nível lógico alto se houver erro em um dos bits recebidos.

Analise abaixo os diagramas esquemáticos dos dois circuitos projetados.

Sobre os circuitos acima, e considerando-se as especificações de cada um, é correto afirmar que:

A forma de onda que corresponde corretamente à saída X do circuito mostrado é:

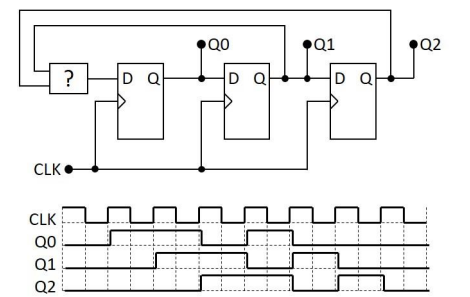

O circuito cujo diagrama esquemático abaixo apresenta um circuito composto por três flip-flops e uma porta lógica desconhecida.

Para que o circuito funcione conforme o diagrama temporal acima, o bloco marcado com uma interrogação deve ser

substituído por uma porta:

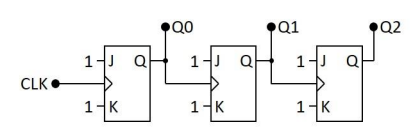

Sabendo-se que, em um determinado instante, o valor binário das saídas Q2Q1Q0, tomadas nessa ordem, é igual a 010, qual o valor binário das saídas após 5 ms?

Analise as afirmativas abaixo quanto aos dispositivos lógicos programáveis (PLD):

I. Um PLD do tipo arranjo lógico programável (PLA) tem um arranjo de portas AND/OR e são programáveis com a queima de fusíveis em uma matriz, com a vantagem de serem totalmente reprogramáveis.

II. Os dispositivos lógicos programáveis complexos (CPLD) que empregam tecnologia de programação EEPROM são apagáveis, reprogramáveis e não voláteis.

III. PLDs do tipo matrizes de portas programáveis em campo (FPGA) podem utilizar uma tabela de consulta (LUT) para criar as funções combinacionais desejadas, sendo que uma LUT de N entradas funciona como uma tabela-verdade para 2N-1 combinações possíveis.

IV. Os FPGAs baseados em SRAM necessitam, para a sua configuração, de uma memória externa cujo conteúdo é transferido para o FPGA quando o dispositivo é energizado.

V. Uma diferença entre CPLD e FPGA é que, no primeiro, os recursos internos de roteamento de sinal lógico programável tendem a ser uniformes em todo o chip, produzindo atrasos de sinal consistentes, enquanto que, no segundo, tendem a ser bem variados, com extensões de caminhos diferentes disponíveis e, portanto, atrasos diferentes.

Sobre as afirmativas acima, é correto afirmar que: